RISV-V下OpenXiangShan和NutShell开源处理器CSR部分差异初探

OpenXiangShan和NutShell是当前较为热门且开源的RISC-V处理器,NutShell整体较为简单,为UCAS一生一芯项目的作品,本文的主要目的是分析NutShell和OpenXiangShan的CSR部分的区别。

主要分析和使用的是:

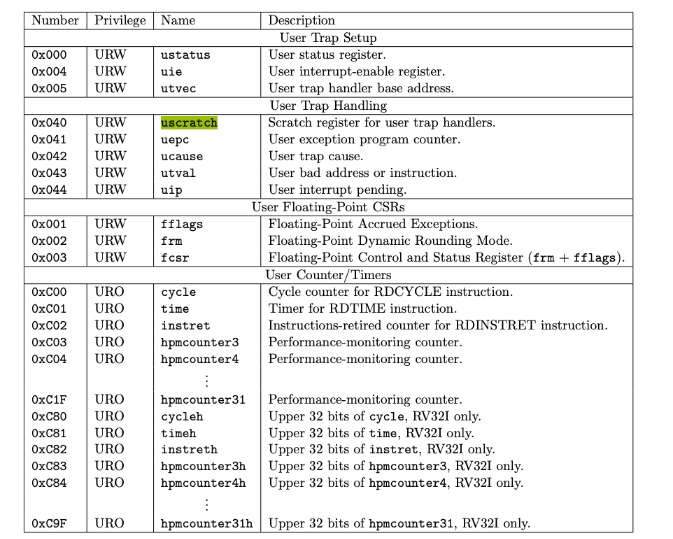

- The RISC-V Instruction Set Manual Volume I: Unprivileged ISA Document Version 20191213

- The RISC-V Instruction Set Manual Volume II: Privileged Architecture Document Version 20211203

ZiCSR指令全部实现。当然这也是必须的。

支持的CSR寄存器

NutShell

NutShell 默认支持以下的 CSR 寄存器:

1 | |

其中U模式在The RISC-V Instruction Set Manual Volume I: Unprivileged ISA Document Version 20190608-Base-Ratified中仍存在,在最新20211203已不存在。

且NutShell中并未实际实现。

OpenXiangShan

LJW:香山的CSR就是多了一些自定义的寄存器,手册要求必须实现的部分是一样的,要是图简单的话就在nutshell上搞就可以。

OpenXiangShan中期待实现的寄存器:

1 | |

1 | |

RISV-V下OpenXiangShan和NutShell开源处理器CSR部分差异初探

http://0vo.lol/2022/10/14/RISV-V下OpenXiangShan和NutShell开源处理器CSR部分差异初探/