RISC-V 特权指令的一些随笔

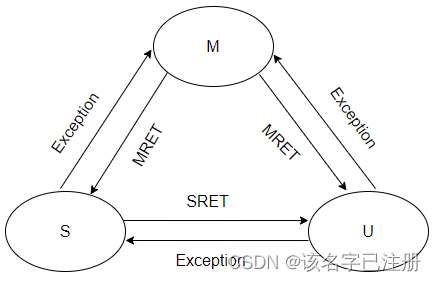

三个模式相互切换的操作

部分摘自:https://blog.csdn.net/m0_67403188/article/details/126080659

MStatus

当使用mret从trap中返回。会根据MPP的值来确定返回的新的特权模式,然后硬件改写mstatus中的MPP=0,MIE=MPIE,MPIE=进trap前的MIE,并设置PC=MEPC。

MCause

Machine Cause Register寄存器是一个mxlen位的读写寄存器。当一个trap被带入m模式时,mcause被硬件写入一个代码,指示导致该trap的事件。如果trap是由中断引起的,则设置mcause寄存器中的中断bit位。

MTVEC

MTVEC用于存储Trap处理程序的地址。就是存储中断向量表的基地址。

当MODE=Direct时,所有进入机器模式的trap都会导致pc被设置为BASE字段中的地址。当MODE= vector时,所有进入机器模式的同步异常都会导致pc被设置为BASE字段中的地址,而异步中断会导致pc被设置为BASE字段中的地址加上中断cause数的四倍。

MEPC(Machine Exception Program Counter)

它保存导致trap的指令的地址。

MIE

中断使能寄存器,区别于mstatus.MIE作为全局控制,MIE是局部控制。

MEIE:M模式外部中断使能位

SEIE:S模式外部中断使能位

MTIE:M模式timer中断使能位

STIE:S模式外部中断使能位

MSIE:M模式软中断使能位

SSIE:S模式软中断使能位

MIP

中断挂起寄存器,包含关于挂起中断的信息。

原文博主的理解:当正在处理一个中断,并且mie关掉中断时,同时设置了mip,此时产生了另一个中断则其会被pending,则MIP里对应的中断信息会被记录。(多个中断?)

MEIP:M模式外部中断挂起位

SEIP:S模式外部中断挂起位

MTIP:M模式timer中断挂起位

STIP:S模式外部中断挂起位

MSIP:M模式软中断挂起位

SSIP:S模式软中断挂起位

MSCRATCH

mscratch 寄存器用于机器模式下的程序临时保存某些数据。mscratch 寄存器可以提供一

种快速的保存和恢复机制。譬如,在进入机器模式的异常处理程序后,将应用程序的某个通

用寄存器的值临时存入 mscratch 寄存器中,然后在退出异常处理程序之前,将 mscratch 寄

存器中的值读出恢复至通用寄存器。